CMOS是單詞的首字母縮寫,集成電路是一塊微小的硅片,它包含有幾百萬個電子元件。術語IC隱含的含義是將多個單獨的集成電路集成到一個電路中,產生一個十分緊湊的器件。在通常的術語中,集成電路通常稱為芯片,而為計算機應用設計的IC稱為計算機芯片。

雖然制造集成電路的方法有多種,但對于數字邏輯電路而言CMOS是主要的方法。桌面個人計算機、工作站、視頻游戲以及其它成千上萬的其它產品都依賴于CMOS集成電路來完成所需的功能。當我們注意到所有的個人計算機都使用專門的CMOS芯片,如眾所周知的微處理器,來獲得計算性能時, CMOS IC的重要性就不言而喻了。CMOS之所以流行的一些原因為:

1、邏輯函數很容易用CMOS電路來實現。

2、CMOS允許極高的邏輯集成密度。其含義就是邏輯電路可以做得非常小,可以制造在極小的面積上。

3、用于制造硅片CMOS芯片的工藝已經是眾所周知,并且CMOS芯片的制造和銷售價格十分合理。

這些特征及其它特征都為CMOS成為制造IC的主要工藝提供了基礎。CMOS可以作為學習在電子網絡中如何實現邏輯功能的工具。CMOS它允許我們用簡單的概念和模型來構造邏輯電路。而理解這些概念只需要基本的電子學概念。

分析cmos電路邏輯的系列及主要參數

1.分析cmos電路邏輯的系列

CMOS集成電路誕生于20世紀60年代末,經過制造工藝的不斷改進,在應用的廣度上已與TTL平分秋色,它的技術參數從總體上說,已經達到或接近TTL的水平,其中功耗、噪聲容限、扇出系數等參數優于TTL。CMOS集成電路主要有以下幾個系列。

(1)基本的CMOS——4000系列。

這是早期的CMOS集成邏輯門產品,工作電源電壓范圍為3~18V,由于具有功耗低、噪聲容限大、扇出系數大等優點,已得到普遍使用。缺點是工作速度較低,平均傳輸延遲時間為幾十ns,最高工作頻率小于5MHz。

(2)高速的CMOS——HC(HCT)系列。

該系列電路主要從制造工藝上作了改進,使其大大提高了工作速度,平均傳輸延遲時間小于10ns,最高工作頻率可達50MHz。HC系列的電源電壓范圍為2~6V。HCT系列的主要特點是與TTL器件電壓兼容,它的電源電壓范圍為4.5~5.5V。它的輸入電壓參數為VIH(min)=2.0V;VIL(max)=0.8V,與TTL完全相同。另外,74HC/HCT系列與74LS系列的產品,只要最后3位數字相同,則兩種器件的邏輯功能、外形尺寸,引腳排列順序也完全相同,這樣就為以CMOS產品代替TTL產品提供了方便。

(3)先進的CMOS——AC(ACT)系列

該系列的工作頻率得到了進一步的提高,同時保持了CMOS超低功耗的特點。其中ACT系列與TTL器件電壓兼容,電源電壓范圍為4.5~5.5V。AC系列的電源電壓范圍為1.5~5.5V。AC(ACT)系列的邏輯功能、引腳排列順序等都與同型號的HC(HCT)系列完全相同。

2.cmos電路邏輯的主要參數

cmos電路邏輯主要參數的定義同TTL電路,下面主要說明cmos電路邏輯主要參數的特點。

(1)輸出高電平VOH與輸出低電平VOL。CMOS門電路VOH的理論值為電源電壓VDD,VOH(min)=0.9VDD;VOL的理論值為0V,VOL(max)=0.01VDD。所以CMOS門電路的邏輯擺幅(即高低電平之差)較大,接近電源電壓VDD值。

(2)閾值電壓Vth。從CMOS非門電壓傳輸特性曲線中看出,輸出高低電平的過渡區很陡,閾值電壓Vth約為VDD/2。

(3)抗干擾容限。CMOS非門的關門電平VOFF為0.45VDD,開門電平VON為0.55VDD。因此,其高、低電平噪聲容限均達0.45VDD。其他CMOS門電路的噪聲容限一般也大于0.3VDD,電源電壓VDD越大,其抗干擾能力越強。

(4)傳輸延遲與功耗。CMOS電路的功耗很小,一般小于1 mW/門,但傳輸延遲較大,一般為幾十ns/門,且與電源電壓有關,電源電壓越高,CMOS電路的傳輸延遲越小,功耗越大。前面提到74HC高速CMOS系列的工作速度己與TTL系列相當。

(5)扇出系數。因CMOS電路有極高的輸入阻抗,故其扇出系數很大,一般額定扇出系數可達50。但必須指出的是,扇出系數是指驅動CMOS電路的個數,若就灌電流負載能力和拉電流負載能力而言,CMOS電路遠遠低于TTL電路。

分析cmos電路邏輯是在TTL電路問世之后 ,所開發出的第二種廣泛應用的數字集成器件,從發展趨勢來看,由于制造工藝的改進,CMOS電路的性能有可能超越TTL而成為占主導地位的邏輯器件 。CMOS電路的工作速度可與TTL相比較,而它的功耗和抗干擾能力則遠優于TTL。此外,幾乎所有的超大規模存儲器件 ,以及PLD器件都采用CMOS藝制造,且費用較低。 早期生產的CMOS門電路為4000系列 ,隨后發展為4000B系列。當前與TTL兼容的CMOS 器件如74HCT系列等可與TTL器件交換使用。

分析cmos電路邏輯-MOS管參數

1.開啟電壓VT

開啟電壓(又稱閾值電壓):使得源極S和漏極D之間開始形成導電溝道所需的柵極電壓;·標準的N溝道MOS管,VT約為3~6V;·通過工藝上的改進,可以使MOS管的VT值降到2~3V。

2. 直流輸入電阻RGS

即在柵源極之間加的電壓與柵極電流之比,這一特性有時以流過柵極的柵流表示,MOS管的RGS可以很容易地超過1010Ω。

3. 漏源擊穿電壓BVDS

在VGS=0(增強型)的條件下 ,在增加漏源電壓過程中使ID開始劇增時的VDS稱為漏源擊穿電壓BVDS

ID劇增的原因有下列兩個方面:

(1)漏極附近耗盡層的雪崩擊穿

(2)漏源極間的穿通擊穿

有些MOS管中,其溝道長度較短,不斷增加VDS會使漏區的耗盡層一直擴展到源區,使溝道長度為零,即產生漏源間的穿通,穿通后源區中的多數載流子,將直接受耗盡層電場的吸引,到達漏區,產生大的ID 。

4. 柵源擊穿電壓BVGS

在增加柵源電壓過程中,使柵極電流IG由零開始劇增時的VGS,稱為柵源擊穿電壓BVGS。

5. 低頻跨導gm

在VDS為某一固定數值的條件下 ,漏極電流的微變量和引起這個變化的柵源電壓微變量之比稱為跨導。gm反映了柵源電壓對漏極電流的控制能力,是表征MOS管放大能力的一個重要參數。一般在十分之幾至幾mA/V的范圍內 。

6. 導通電阻RON

導通電阻RON說明了VDS對ID的影響 ,是漏極特性某一點切線的斜率的倒數,在飽和區,ID幾乎不隨VDS改變,RON的數值很大 ,一般在幾十千歐到幾百千歐之間,由于在數字電路中 ,MOS管導通時經常工作在VDS=0的狀態下,所以這時的導通電阻RON可用原點的RON來近似。對一般的MOS管而言,RON的數值在幾百歐以內 。

7. 極間電容

三個電極之間都存在著極間電容:柵源電容CGS 、柵漏電容CGD和漏源電容CDS

CGS和CGD約為1~3pF

CDS約在0.1~1pF之間。

8. 低頻噪聲系數NF

噪聲是由管子內部載流子運動的不規則性所引起的,由于它的存在,就使一個放大器即便在沒有信號輸人時,在輸出端也出現不規則的電壓或電流變化,噪聲性能的大小通常用噪聲系數NF來表示,它的單位為分貝(dB)。這個數值越小,代表管子所產生的噪聲越小,低頻噪聲系數是在低頻范圍內測出的噪聲系數。場效應管的噪聲系數約為幾個分貝,它比雙極性三極管的要小 。

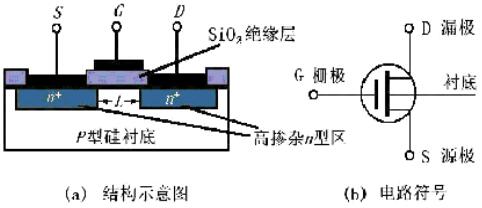

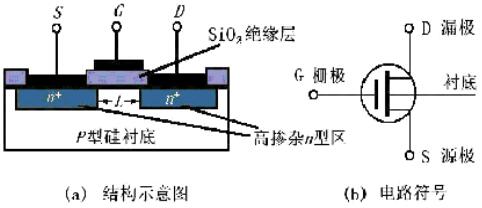

分析cmos電路邏輯結構

分析cmos電路邏輯是在TTL電路問世之后 ,所開發出的第二種廣泛應用的數字集成器件,從發展趨勢來看,由于制造工藝的改進,CMOS電路的性能有可能超越TTL而成為占主導地位的邏輯器件 。CMOS電路的工作速度可與TTL相比較,而它的功耗和抗干擾能力則遠優于TTL。此外,幾乎所有的超大規模存儲器件 ,以及PLD器件都采用CMOS藝制造,且費用較低。早期生產的CMOS門電路為4000系列 ,隨后發展為4000B系列。當前與TTL兼容的CMO器件如74HCT系列等可與TTL器件交換使用。下面首先討論CMOS反相器,然后介紹其他cmos電路邏輯。

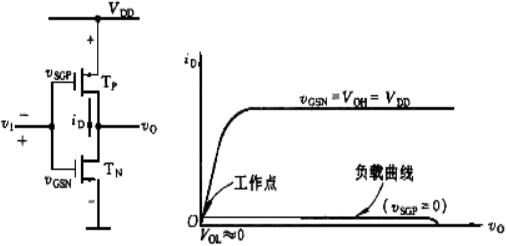

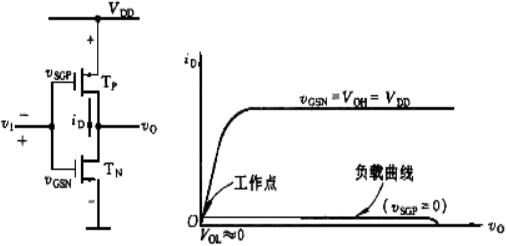

工作原理

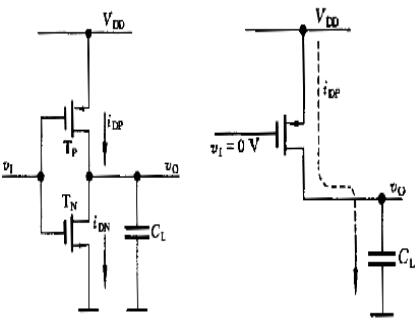

首先考慮兩種極限情況:當vI處于邏輯0時 ,相應的電壓近似為0V;而當vI處于邏輯1時,相應的電壓近似為VDD。假設在兩種情況下N溝道管 TN為工作管P溝道管TP為負載管。但是,由于電路是互補對稱的,這種假設可以是任意的,相反的情況亦將導致相同的結果。

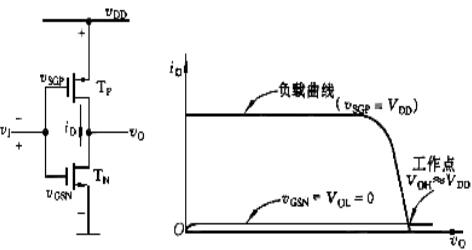

下圖分析了當vI=VDD時的工作情況。在TN的輸出特性iD—vDS(vGSN=VDD)(注意vDSN=vO)上 ,疊加一條負載線,它是負載管TP在 vSGP=0V時的輸出特性iD-vSD。由于vSGP<VT(VTN=|VTP|=VT),負載曲線幾乎是一條與橫軸重合的水平線。兩條曲線的交點即工作點。顯然,這時的輸出電壓vOL≈0V(典型值<10mV ,而通過兩管的電流接近于零。這就是說,電路的功耗很小(微瓦量級)

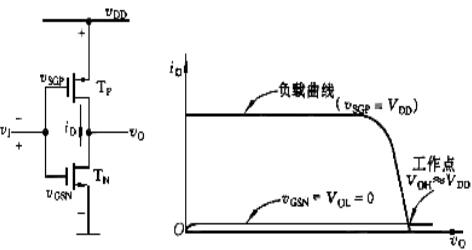

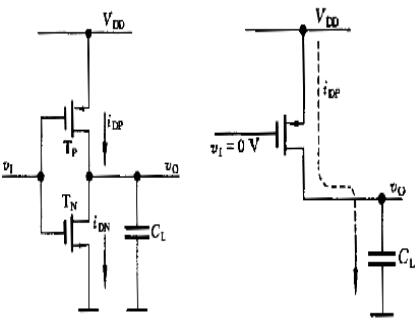

下圖分析了另一種極限情況,此時對應于vI=0V。此時工作管TN在vGSN=0的情況下運用,其輸出特性iD-vDS幾乎與橫軸重合 ,負載曲線是負載管TP在vsGP=VDD時的輸出特性iD-vDS。由圖可知,工作點決定了VO=VOH≈VDD;通過兩器件的電流接近零值 。可見上述兩種極限情況下的功耗都很低。

由此可知,基本CMOS反相器近似于一理想的邏輯單元,其輸出電壓接近于零或+VDD,而功耗幾乎為零。

傳輸特性

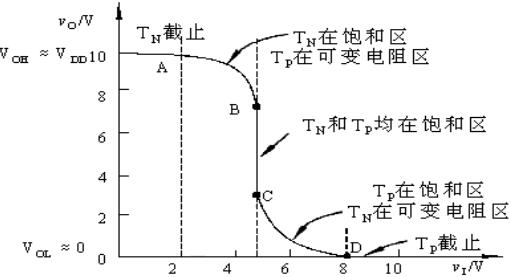

下圖為CMOS反相器的傳輸特性圖。圖中VDD=10V,VTN=|VTP|=VT=2V。由于 VDD>(VTN+|VTP|),因此,當VDD-|VTP|>vI>VTN 時,TN和TP兩管同時導通。考慮到電路是互補對稱的,一器件可將另一器件視為它的漏極負載。還應注意到,器件在放大區(飽和區)呈現恒流特性,兩器件之一可當作高阻值的負載。因此,在過渡區域,傳輸特性變化比較急劇。兩管在VI=VDD/2處轉換狀態。

工作速度

CMOS反相器在電容負載情況下,它的開通時間與關閉時間是相等的,這是因為電路具有互補對稱的性質。下圖表示當vI=0V時 ,TN截止,TP導通,由VDD通過TP向負載電容CL充電的情況。由于CMOS反相器中,兩管的gm值均設計得較大,其導通電阻較小,充電回路的時間常數較小。類似地,亦可分析電容CL的放電過程。CMOS反相器的平均傳輸延遲時間約為10ns。

烜芯微專業制造二三極管,MOS管,20年,工廠直銷省20%,1500家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹

烜芯微專業制造二三極管,MOS管,20年,工廠直銷省20%,1500家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經理給您精準的報價以及產品介紹