數字信號處理的出現改變了信息與信號處理技術,而數據采集作為數字信號處理的前期工作,在整個數字系統中起到關鍵性作用。數據采集是指對設備被測的模擬或數字信號,自動采集并送到上位機中進行分析、處理。數據采集卡,即實現數據采集功能的計算機擴展卡,可以通過USB、PXI、PCI、PCI Express、火線(1394)、PCMCIA、ISA、Compact Flash、485、232、以太網、各種無線網絡等總線接入計算機。本文介紹了一種基于FPGA設計的數據采集卡。

1.數據采集系統

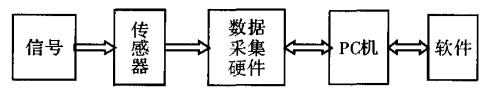

數據采集是指從待測設備中自動采集信息的過程。圖1顯示了基于PC機的典型數據采集系統的各項組成部分。選用PC機作為控制系統操作平臺,為了能和外部設備通信,PC機提供了外置的USB、串口、并口及內置的ISA、PCI等接口。PCI總線接口速度快、系統占用率低,有完備的即插即用管理體制,是目前計算機插卡式外設總線的事實標準。本文利用FPGA通過PCI接口芯片與計算機進行通信,FPGA外接FIFO存儲器,A/D轉換數據直接存儲在FIFO中,實現了數據的高速采集與連續穩定數據流的輸出。

圖1 典型數據采集系統

2.數據采集硬件設計

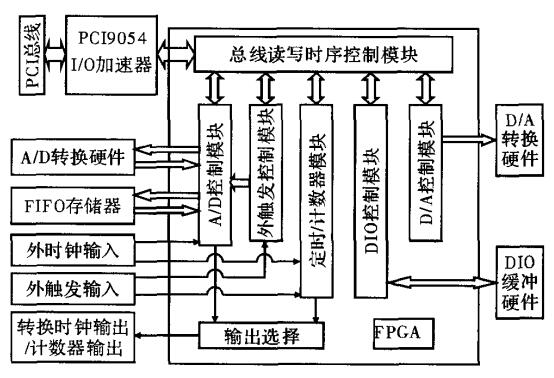

PCI數據采集板卡的硬件整體框架如圖2所示。

圖2 系統硬件框圖

2.1PCI總線接口設計

PCI總線是一個地址/數據、命令/字節選擇信號復用的總線。它采用主從信號雙向握手的方式來控制數據的傳輸,其接口電路設計和傳統總線接口電路設計有較大的差別,所以必須嚴格遵守PCI總線規范所規定的技術規范。本文采用PLX公司的PC19054作為PCI總線的接口控制器。PCI9054是專用的PCI接口芯片,它主要是將復雜的PCI時序轉換為簡單的時序。

2.2FPGA設計

FPGA設計用超高速集成電路硬件描述語言(VeryHighSpeedIntegratedCircuithardwareDessriptionLanguage,VHDL)實現,設計軟件選用QuartusII。VHDL設計主要分為:總線讀寫設計,A/D控制設計,D/A控制設計,定時/計數器設計及DIO設計。

(1)總線讀寫設計

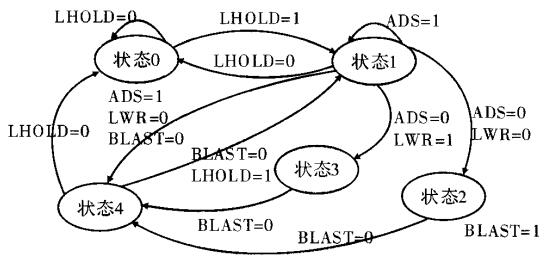

總線讀寫設計是FPGA設計的頂層模塊,主要完成PCI9054與本地的通信,實現數據的正確傳輸。PCI9054單周期讀、寫和DMA讀的VHDL語言時序控制狀態機如圖3所示。狀態0為空閑狀態,狀態1為總線保持狀態,狀態2為DMA讀狀態,狀態3為單周期寫狀態,狀態4為讀寫操作完成狀態。

圖3 本地總線狀態機設計

(2)控制信號說明

ADS#:地址選通信號,雙向。表示地址有效及新的總線訪問周期的開始,在總線訪問周圍的第一個時鐘周期有效。BLAST#:突發傳輸結束信號,雙向。由當前本地總線主動方驅動,用來表明總線傳輸的最后一個數據傳輸。LW/R#:寫/讀信號,雙向。低位讀,高為寫。LHOLD:保持總線請求,輸出。請求使用本地總線。當控制可以實現時,本地總線仲裁回應LHOLDA。

(3)A/D控制設計

A/D控制是數據采集卡的主要部分,設計主要包括:A/D采樣時鐘的產生,分組采集控制,觸發設置及FIFO讀寫控制等。

(a)A/D采樣時鐘的產生。采樣時鐘的產生主要是根據設定的采樣頻率產生具有一定低脈寬的信號,這是為了在轉換完成時能正確地讀出轉換數據。值得注意的是,在FIFO溢出的情況下及分組采集的組間間隔時間段內要停止輸出采集脈沖。

(b)分組采集控制。分組采集是按照內外時鐘源分別進行設計的。首先根據組循環次數及首末通道設置計算出一組內總共要采集的點數,即:一組內總共要采集的點數=(末通道-首通道+1)*組循環次數。

在內時鐘模式下,啟動A/D轉換后,在每次轉換完成后采集點數加1,直至加到一組內總共要采集點數為止,此時停止輸出轉換脈沖,而后進入組問間隔時間,開始對基準時鐘進行計數,計到設定的組間間隔值后輸出轉換脈沖,再次進入轉換計數周期,依此重復下去。

在外時鐘模式下,當檢測到外時鐘下降沿時開始輸出轉換脈沖并在轉換完成后進行計數,直至加到一組內總共要采集的點數為止,此時停止輸出轉換脈沖,當再次出現外時鐘的下降沿時,便開始新的一組分組采集。

(c)觸發設置。觸發設置是根據板卡控制字中的觸發源、觸發方向及觸發類型共同決定的。

(d)FIFO讀寫控制。FIFO的讀是由PCI9054發起的,在PCI9054讀周期,在滿足地址條件的情況下,產生FIFO的讀信號,將A/D數據傳輸到主機。

FIFO的寫信號是由A/D芯片的STS信號控制的,當STS信號由高變為低時表示本次轉換完成,且數據線上數據有效,而FIFO是在下降沿啟動寫周期,上升沿將數據打入FIFO中,因此只需將STS信號取反后賦給FIFO的寫信號。

3.硬件設計的測試

在板卡的設計過程中,硬件設計的測試是按如下步驟進行的:首先通過功能仿真及時序仿真排除設計上的大部分錯誤;其次通過PCItree軟件進行測試,通過簡單的功能測試,如開關量輸入輸出;然后通過簡易演示程序測試;最后通過高級程序的全面測試。在不同的測試階段會發現各種設計問題,再將設計回歸到功能仿真及時序仿真,反復修改完善程序,直到最終滿足功能設計要求。

結束語

本文總結了基于FPGA的PCI數據采集卡的設計方案,該板卡實現了查詢、中斷和DMA等多種方式讀取數據,可實時采集數據,實現大容量數據的緩存,有效地解決對數據高速采集和傳輸的需求。可直接插在PC機或與之兼容的計算機內任一PCI插槽中,構成各領域的數據采集、波形分析和處理系統,也可構成工業生產過程監控系統。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹