短溝道效應解析

在 MOS 晶體管領域,當溝道長度縮至與漏結及源結耗盡層厚度相近時,一系列有別于長溝道 MOS 管特性的現象便會顯現,這些現象被統稱為短溝道效應,其根源在于溝道區二維電勢分布的形成以及高電場的出現。

當 MOSFET 的溝道長度低于 3 微米時,短溝道效應便較為突出。此類效應的產生主要受以下五種因素影響,這些因素皆源于理想按比例縮小理論的偏離:

一是電源電壓未能按比例縮小,致使電場強度增大。

二是內建電勢既無法按比例縮小,又不可忽視。

三是源漏結深難以按比例減小。

四是襯底摻雜濃度的上升造成載流子遷移率降低。

五是亞閾值斜率無法按比例縮小。

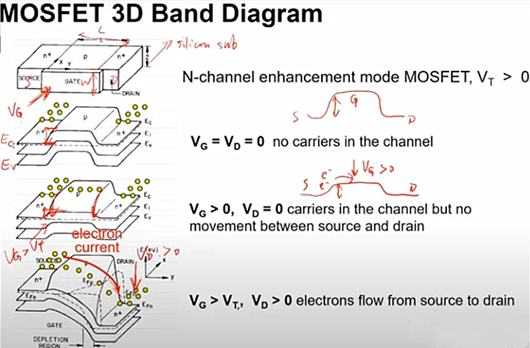

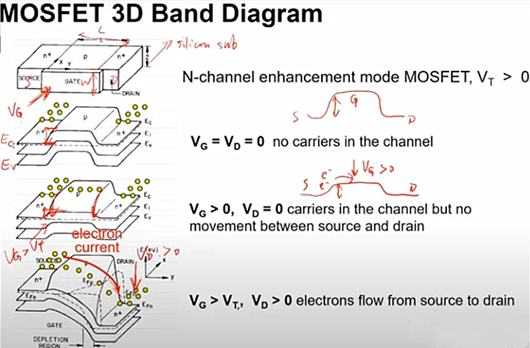

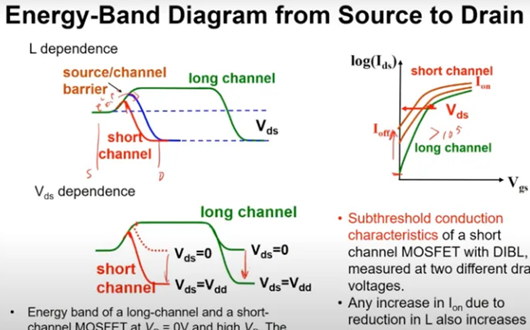

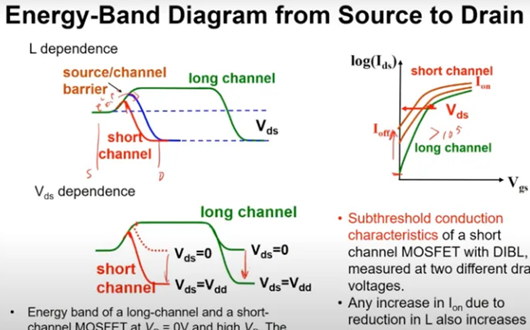

以下借助 MOSFET 3D 能帶圖,深入剖析短溝道效應。以 NMOS 為例,當施加 Vgs 電壓時,在 Gate 表面,能帶向下彎曲(如圖第三個圖例所示),這使得電子更易穿越溝道。然而,由于此時 Drain 尚未加壓,能帶位置保持不變,因此并無電流流過。

一旦給 Drain 加壓(對應圖中第四個圖例),Drain 處能帶向下彎曲,從 Source 經 Channel 至 Drain 形成能級差,電子得以沿此路徑流動。

從能帶圖視角審視短溝道效應,可得出以下結論:

對于短溝道(L 極小)的 MOS 管,Source 與 Drain 距離過近,Channel 能帶被向下拉,使得處于 Cut-Off 狀態的器件 leakage 增大。這是因為溝道勢壘降低,熱激發電子在常溫下更易越過勢壘,從 Source 漂移到 Drain,這一效應顯著影響亞閾值漏電流。

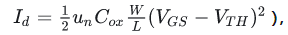

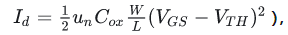

若提升 Vds 值,由于 Source 與 Drain 距離過近,Drain 勢壘下降會引發 Channel 勢壘降低,導致溝道電流 Id 對 Vds 的敏感性增強,這便是所謂的漏誘生勢壘降低效應(DIBL)。

因此,若要借助減小溝道 L 值來提升開啟電流,需警惕短溝道效應致使 MOS 管關斷電流呈指數級增長的風險。

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280