開漏Open-drain與推挽push-pull介紹

開漏(Open-Drain)與推挽(Push-Pull)輸出是兩種關鍵的輸出方式,它們各自具有獨特的原理、應用場景以及優缺點,以下將對這兩種輸出技術進行詳細且專業的闡述。

開漏(Open-Drain)與推挽(Push-Pull)輸出是兩種關鍵的輸出方式,它們各自具有獨特的原理、應用場景以及優缺點,以下將對這兩種輸出技術進行詳細且專業的闡述。

一、開漏輸出

(一)工作原理

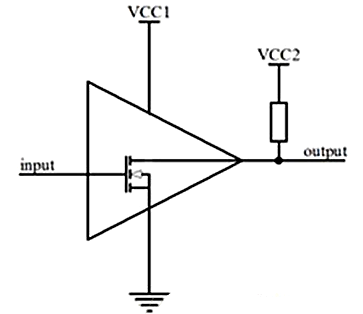

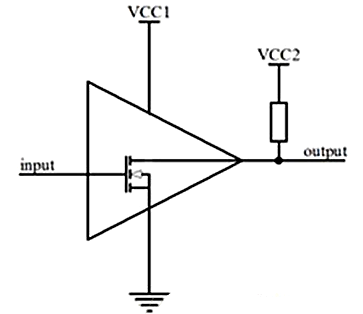

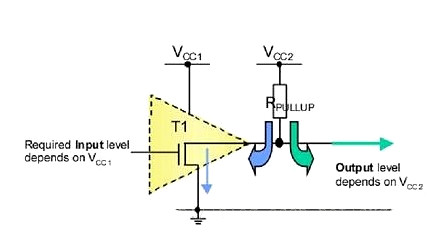

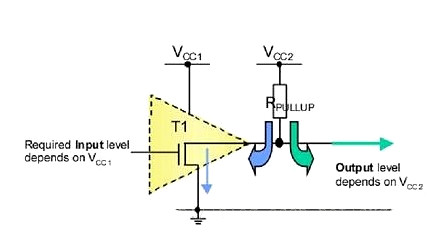

開漏電路以內置的N溝道MOSFET的漏極作為輸出端,該MOSFET連接在內部輸出與地之間。當柵極輸入低電平(0)時,NMOS的漏極與源極導通,此時輸出端呈現低電平(0);而當柵極輸入高電平(1)時,NMOS處于不導通狀態,輸出端呈現高阻態,表現為高電平(1),但這一高電平狀態需要外部上拉電路來維持,且其上升沿相對較為緩慢。

開漏輸出的輸出電壓由外接的Vcc決定,Vcc既可高于輸入高電平電壓(實現向上電平轉換),也可低于輸入高電平電壓(實現向下電平轉換)。與推挽輸出相比,開漏輸出結構更為簡單,僅包含底部的N溝道MOSFET,缺少頂部的P溝道MOSFET,因此無法自主輸出高電平,必須借助外部上拉電阻來實現高電平輸出。

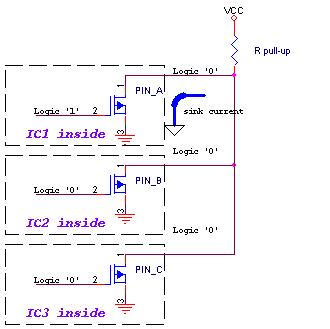

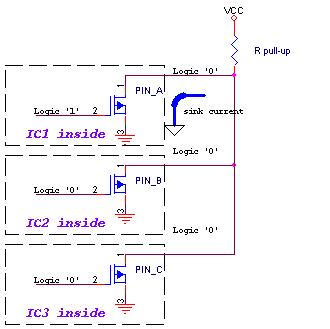

開漏輸出僅具備漏電流(sinkcurrent)能力,若需實現集電流(sourcecurrent),則必須外接上拉電阻。這一特性使得開漏輸出在特定應用場景中具有獨特優勢,但同時也對其使用提出了一定要求。

(二)優點

在不同電壓節點間的電平轉換方面表現出色,能夠靈活地實現向上電平轉換(Up-translate)和向下電平轉換(Down-translate),為多種電壓標準的電路系統之間的信號傳輸提供了有效的解決方案。

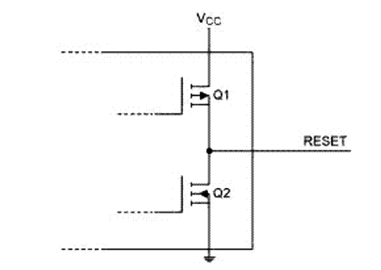

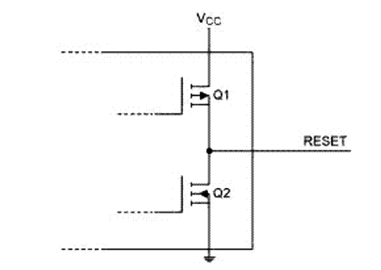

支持“線與”(Wired-AND)邏輯功能,允許多個開漏輸出的Pin腳連接到同一條信號線上。只要其中一個輸出為低電平,整個線上的邏輯狀態即為低電平,這一特性在I2C、SMBus等總線系統中被廣泛應用,用于判斷總線的占用狀態以及實現多設備間的通信協調。

可有效利用外部電路的驅動能力,從而減輕IC內部的驅動負擔。當IC內部的MOSFET導通時,驅動電流從外部的VCC經過上拉電阻、MOSFET流向GND,IC內部僅需提供較小的柵極驅動電流,這有助于降低IC的功耗并提高其驅動能力。

通過改變外接上拉電源的電壓,可靈活調整傳輸電平。例如,IC的邏輯電平由其自身的電源Vcc1決定,而輸出高電平則可由另一電源Vcc2決定,從而實現低電平邏輯控制輸出高電平邏輯的功能,為電路設計提供了更大的靈活性。

(三)缺點

若開漏Pin未連接外部上拉電阻,則只能輸出低電平,無法實現高電平輸出,這限制了其在某些需要獨立高電平輸出場景中的應用,必須外加上拉電阻才能完整地實現高低電平輸出功能。

連接上拉電阻的線路在電壓提升過程中,其最快上升速度受到電阻R與寄生電容(包括Pin腳電容和板級電容)的限制,遵循R×C時間常數規律。這意味著信號的上升時間與上拉電阻的阻值密切相關,阻值越大,上升時間越長,信號傳輸速度越慢。

當輸出電平為低時,N溝道MOSFET導通,導致Vcc與GND之間形成一個持續的電流回路,電流流經上拉電阻和MOSFET,從而影響整個系統的功耗。為了減小這一電流,可采用較大阻值的上拉電阻,但這又會使輸出信號的上升時間變慢。因此,在選擇上拉電阻阻值時需要在功耗與信號傳輸速度之間進行權衡,較大的阻值可降低功耗但會降低信號速度,反之則會增加功耗但提高信號速度。同時,上拉電阻的阻值也不能過小,因為在輸出低電平時,過小的阻值會使MOSFET需要承受更大的漏極電流,進而導致更高的功耗。

二、推挽輸出

(一)工作原理

推挽輸出電路在輸出腳內部集成了互補的MOSFET對,即高側的P溝道MOSFET(PMOS)和低側的N溝道MOSFET(NMOS)。當柵極輸入低電平(0)時,高側PMOS處于高阻態,低側NMOS導通,此時輸出端呈現低電平(0);而當柵極輸入高電平(1)時,高側PMOS導通,低側NMOS處于高阻態,輸出端呈現高電平(1)。這種通過交替導通高側和低側MOSFET來輸出高低電平的方式,使得推挽輸出既能漏電流(sinkcurrent)又能集電流(sourcecurrent),并且其輸出的高低電平由IC的電源電壓決定。

推挽輸出通常具有兩種穩定狀態(高電平和低電平)以及一個可選的高阻抗(highimpedance)狀態,但一般情況下,在不需要高阻抗狀態時,無需額外的上拉電阻,這與開漏輸出有所不同。

(二)優點

具備雙向電流傳輸能力,既能吸電流(將電流從負載引導至地),又能貫電流(將電流從電源引導至負載),這使其在驅動各種負載時具有更廣泛的應用范圍和更強的驅動能力。

信號傳輸速度快是推挽輸出的顯著優勢。由于其內部采用兩個互補的晶體管分別負責高電平和低電平的輸出,并且在輸出過程中能夠快速地切換晶體管的導通與截止狀態,因此能夠以較快的速度驅動線路,實現信號的快速傳輸與切換。

與開漏輸出相比,推挽輸出的高低電平由IC自身的電源決定,這使得其在電路設計中具有更高的集成度和更直接的控制方式,但在進行邏輯操作等場景下相對開漏輸出的靈活性可能有所降低。

(三)缺點

在一條總線上,通常只能存在一個推挽輸出的器件,否則容易導致總線沖突和電路故障。這是因為推挽輸出器件在輸出高低電平時會主動驅動信號線,若多個推挽輸出器件同時連接在同一總線上且輸出不同的電平,將產生較大的電流沖擊,損壞器件或導致信號傳輸錯誤。

推挽輸出往往需要消耗較多的電流,相對而言功耗較大。這是由于在輸出過程中,無論是高側還是低側MOSFET導通時都會有一定程度的電流流經,尤其是在驅動較大負載或以較高頻率切換輸出狀態時,功耗問題會更加顯著,這對電池供電或對功耗敏感的系統來說是一個需要重點關注的因素。

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280